Over the last few weeks, I have built several SmartDisk II, and I have been testing the hardware and the latest firmware release on my beloved IIGS.

The IIGS is very easy to work with, and loading GSOS 6.04 immediately reveals any timing issues.

Everything was fine until I received a message from a user explaining that some SmartDisks were working on the IIc Smartport and others were not, though all were working on the IIGS.

I decided to sort this out, so I took all my 10 samples—and guess what? Half of them were not working on the IIc.

Finding the issue was like looking for a needle in a haystack, as the problem was not consistent.

I gathered my courage and reopened the engine. I spent endless hours trying to figure out what was not working.

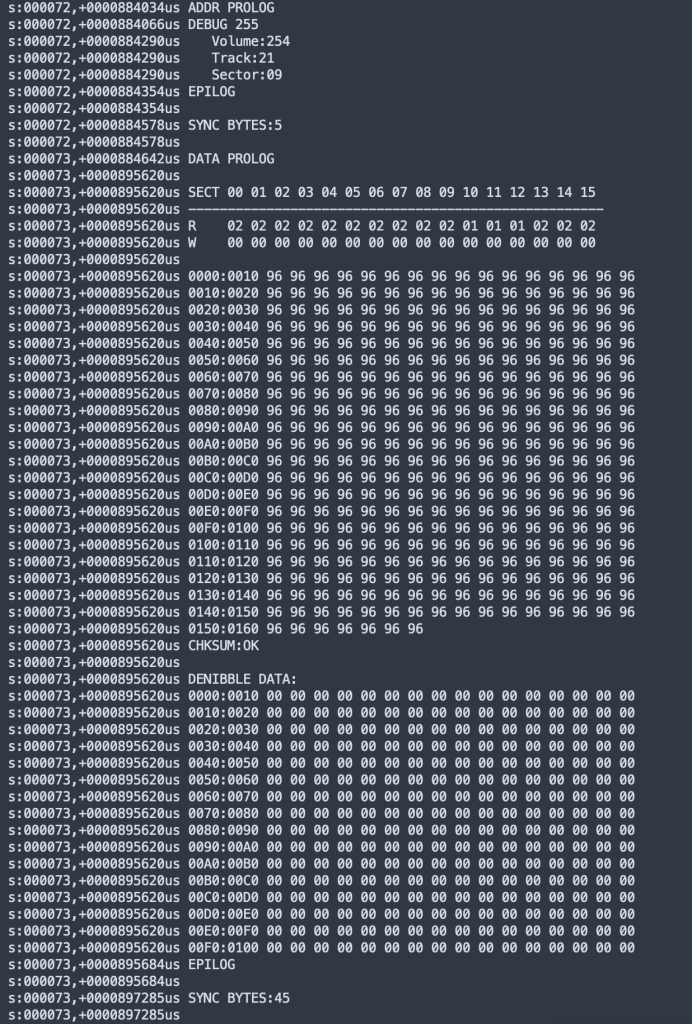

I used my preferred logic analyzer, and for some reason the incoming request from the IIc was sometimes corrupted (checksum failed), and the sent response was erratic (timing fluctuating from 4μs to 5μs).I was scratching my head, with no clue what was happening. I decided to restart the whole process and make the Smartport emulation as accurate as possible.

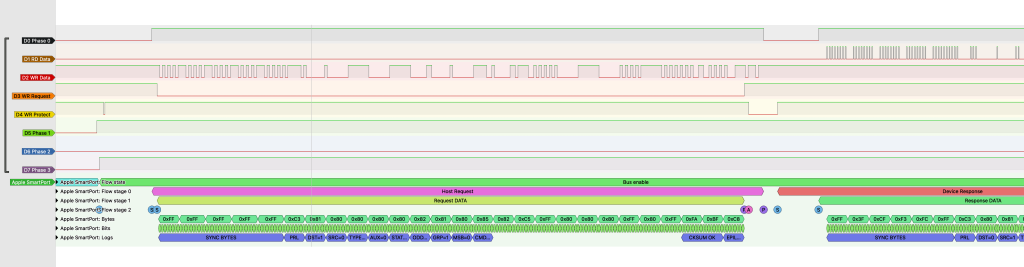

To do so, I was missing an important tool to speed up the analysis: a custom, homemade protocol decoder. Saleae Logic 2 offers a framework based on C; I tried it, but it was not so easy to get started with.

Then I looked at Sigrok Pulseview, DSView which uses a Python-based protocol decoder. It was exactly what I was looking for: simple, straightforward, and with various examples.

I built a complete Smartport data flow protocol decoder using the following pins:•

- Phase 0 -3 Host Request + Bus status

- Write Request: Write Start / Stop

- Write Protect: Device Ack

- RD Data

- Write Data

The good thing with the analyzer is also general log link to event on the screen (cross reference first column 000072 as ex)

I started using the protocol decoder and encountered the same issue on the IIc, but not on the IIGS.

I checked all the pin signals and found that the Select line is free-floating on the IIc, but not on the IIGS. Of course, I had an interrupt attached to it, which meant it was preempting the CPU core for no reason, causing erratic delays.

Sometimes, a small thing can cause endless work

But that was not the only issue. I managed to adapt the code to make the timing perfect, and now it should be perfect from release v0.80.27. I will do some testing before releasing the new firmware.

The DSView / SIgrok protocol analyzer project is available here

https://github.com/vibr77/SigrokPulseView_AppleII_protocolDecoder

I hope you will like it 😉